高速信号回路の「リーン設計技術」

リーン(lean)は、ファット(fat)の対義語で、余分な肉がついておらず、細身で健康な状態を指す形容詞です。

私たちの高速信号回路の設計は、まさにこのリーンな状態を目指しています。

例えば、この部品は本当に必要なのか、BGAからの引き出し配線をよりシンプルにできないか、或いは、もっと小型化・省電力化できないか等を常に考え、余分な肉を落としてゆきます。

私たち独自の高速信号回路の「リーン設計技術」は、従来の対処手法ではなく、本質的な商品の差別化、合理化につながる革新的なアプローチです。

独自の「リーン設計技術」

デジタルTVの創生期からの設計参画による技術蓄積を体系化し、独自の高速信号回路の「リーン設計技術」を確立。7つの最適化手法と、解析と計測による検証手法により、お客様の商品の差別化と、合理化を支援します。

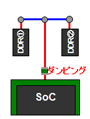

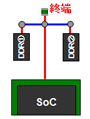

例えば、高速伝送路の設計では、波形の反射の影響を抑えるため、レギュレータと抵抗で整合させることが一般的です。しかしながら、この方法では、部品コストと消費電力のアップが避けられません。

「リーン設計技術」では、従来の設計手法とは大きく異なり、波形の整合ではなく、シンプルに配線を短く、かつ配線インピーダンスを下げることで反射の影響を抑えます。これによりレギュレータと抵抗を削除することができ、かつレイアウト面積も小さくすることが可能になります。

ただし、この設計手法を用いるためには、確実な検証が不可欠です。私たちは、高度なシミュレーション技術と計測技術による確実な検証を通じ、常識を覆す設計を常識にしてゆきます。

リファレンスパターンの最適化設計

一般的に、DDR等の高速信号回路の設計では、半導体メーカー指定のリファレンスを用いるため、商品の差別化や合理化が困難です。独自の高速信号回路の「リーン設計技術」は、従来の慣習や、定石にとらわれない斬新な着想で、リファレンスパターンの最適化を行います。

DDR

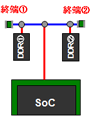

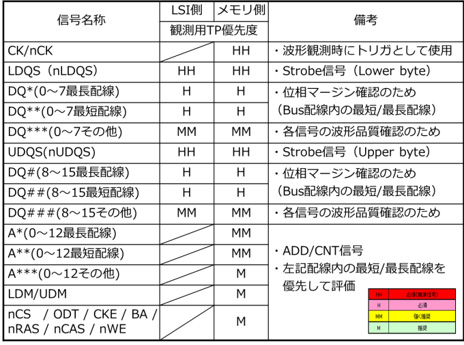

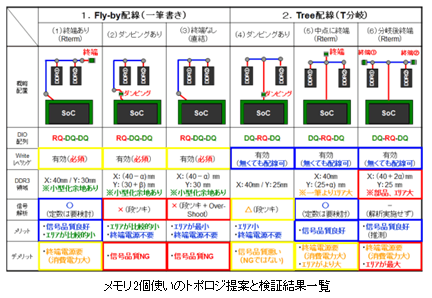

信号品質や要求仕様(面積、電力など)などを満たす設計解をトポロジー検討を用いて求め、反射やクロストーク、ビアやパスコンの配置も考慮したパターン設計を行います。その後、パターン検証によって、所望の波形となっているかや、同時スイッチングノイズやビア間クロストークなど、回路図には現れないリスクまで検証して、安定動作を実現します。

配線のインピーダンス整合、分岐方法、ダンピング抵抗、終端抵抗の有無や定数をパラメータとして解析を行い、信号品質や面積を総合的に判断して、設計解を導出します。

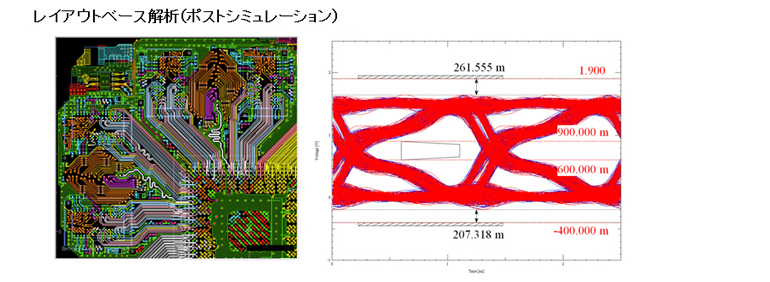

実際のパターンデータから配線、電源ベタ、GNDベタの相互影響をSパラメータとして抽出し、信号のクロストークノイズ、反射ノイズを統合して伝送信号を解析することで、所望の波形となっているか確認します。

差動信号(USB3.0、HDMI、LVDS等)

実際のパターンデータから配線、電源ベタ、GNDベタの相互影響をSパラメータとして抽出し、信号のクロストークノイズ、反射ノイズを統合して伝送信号を解析することで、所望の波形となっているか確認します。

差動信号(USB3.0、HDMI、LVDS等)

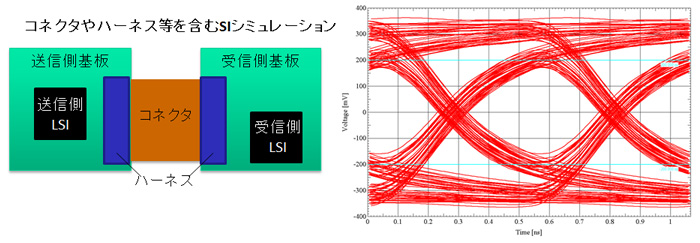

複数の基板にまたがる差動信号の設計では、基板だけでなく、コネクタやハーネスを含めた伝送線路のシミュレーションが必要です。私たちは、システム全体を計算したSIシミュレーションにより、LSIの設計や筐体検討の段階から、システムマージンを満たすコネクタやハーネスを含めた商品全体の配線レイアウトを提案し、仕様に落とし込みます。

設計着手までの流れ

お客様からお伺いしましたご要望・課題に対しまして、こちらから「リーン設計」による改善提案をご提示させていただきます。

ご提案内容につきまして、ご不明な点や、更なるご要望等がございましたら、お互い納得のゆくまで、何度でも打ち合わせをさせていただき、アプローチを整合いたします。

その上で、正式にご依頼をいただき、設計に着手いたします。

また、徹底した情報セキュリティ管理により、情報漏えいの発生を防止しております。なお、お客様のご要望に応じまして、秘密保持契約(NDA)にも対応いたします。

まずは、お気軽にご相談ください。

プリント基板設計・製作

電子回路に精通したメンバーが、お客様の意図を汲み取り、課題解決のためのプリント基板を設計、製作します。

基板製造

パナソニック製基材を使用、国内工場で製造し、お客様のご要望に合わせて最適なラインをご提案します。

- 最短2日で基板製造(片面板~6層板)

- ライン/スペース0.1/0.1mmまで標準対応

- 1枚からご注文可能

※上記日数は土日、祝日は含まれません。

※特殊加工や材料は別途ご相談ください。(例:金メッキ、IVH、鉛フリーベラー、樹脂埋めVia)

部品実装

下表のような様々な形態の部品実装・改造に対応します。

- 国内工場で実装

- 0.5mmピッチBGA、0603チップまで標準対応

- 1台からご注文可能

- 最短2日で実装

豊富な実績

パナソニックの幅広い商品分野での設計実績があります。

家電、AV機器

- 4Kテレビ

- デジタルカメラ

- HD映像コム

住宅設備

- HEMS関連機器

- パワーコンディショナー

- スマートメータ

車載機器

- ADAS関連機器

- ディスプレイオーディオ

- 車載電池関連機器

設計着手までの流れ

お客様からお伺いしましたご要望・課題に対しまして、こちらから「リーン設計」による改善提案をご提示させていただきます。

ご提案内容につきまして、ご不明な点や、更なるご要望等がございましたら、お互い納得のゆくまで、何度でも打ち合わせをさせていただき、アプローチを整合いたします。

その上で、正式にご依頼をいただき、設計に着手いたします。

また、徹底した情報セキュリティ管理により、情報漏えいの発生を防止しております。なお、お客様のご要望に応じまして、秘密保持契約(NDA)にも対応いたします。

まずは、お気軽にご相談ください。

基板設計のご依頼先でお悩みではありませんか?

普通のFR-4は、何℃まで使えますか?

”普通の”が気になりますが、ごく一般のと言う意味でとらえさせて頂き、Panasonic材のR-1705の場合で回答致します。

R-1705の最高使用温度は、120~130℃です。

長時間、上記ギリギリ状態で使用すると茶褐色に変色します。(特に特性的に劣化しているわけではないようですが。。。)

温度以外の条件も関わってくる可能性がありますので、使用環境を考慮し、しっかり評価されることをお薦めします。

基板は、緑色に白色の文字しかできないのでしょうか?

基板が緑色なのは、基板表面に緑色のレジストインクを塗布しているからで、基板工場によっては、他の色のレジストインクを持っているところもあります。我々がお願いしている基板工場では、緑以外に青・白・黒のレジストインクを常備しており、赤・黄も別途費用にて対応可能です。

白色の文字は、シルクと呼ばれ、社名や基板名や部品番号を基板上に表示したい時に使っていますが、こちらも工場によっては他の色のシルクインクを持っているところもあります。我々がお願いしている基板工場では、白以外に黒や黄を常備しています。

回路・プリント基板の設計事例

これまでに実施した電子回路設計、及びプリント基板設計の事例をご紹介します。

品質、コスト、納期の課題を同時に解決します。

- 事例1 地盤低層化

- 事例2 パスコン半減

- 事例3 HDMI改善

- 事例4 DDR設計1

- 事例5 DDR設計2

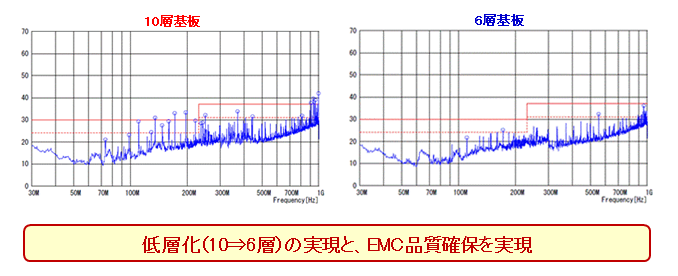

事例1 基板低層化(10層⇒6層)によるコストダウン、EMC品質確保の両立

お客様のご要望

- 10層基板から6層基板に低層化して、コストダウンしたい

- 低層化により予想されるEMC品質低下を避けたい

実施内容

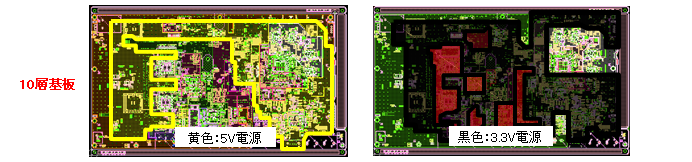

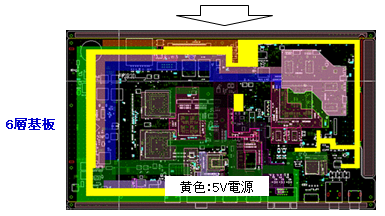

1. 電源層レイアウト見直し

10層基板の電源層の数:2⇒6層化のためには、電源層の数を「1」にすることが必須

目標:

5V電源の面積を減らす

戦略:

5V電源使用部品を基板端に移動し、

基板内側の5V電源面積を減らす

⇒5V電源の面積を約16%に減らし、電源層の一層化を実現

2. ノイズに関するノウハウの活用

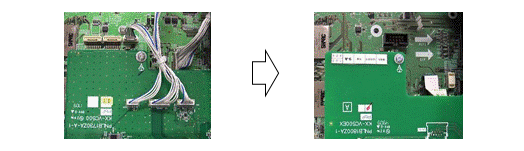

例)ケーブルのアンテナ化、EMCのバラツキ回避

10層基板:ケーブル直下にスイッチング電源

⇒ケーブルがアンテナとなり、スイッチングノイズの輻射要因となってしまう

⇒ケーブルの束ね方のバラツキが、EMC品質のバラツキにつながる

⇒ケーブルからコネクタへの部品変更により、EMC悪化リスクを回避

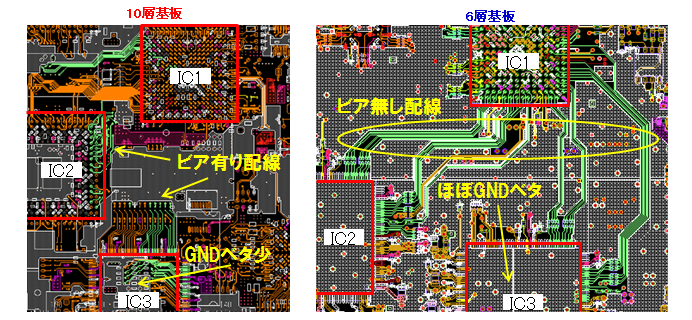

3. IC周辺のノイズ低減設計

- 輻射、信号特性劣化の要因となるビア削減のため、FPGA(IC1)のピン配置見直し

- QFPのIC直下を、できるだけGNDベタにする

⇒IC周辺のノイズ低減設計により、不要輻射を根元から断つ

4.その他EMC設計事例

- DDコンIC変更:高速品から低速品へ

- DDコンレイアウト変更:スイッチング電流のループ経路見直し

- リターンパスの最適化:信号の層移動時のリターンパス確保

- ビアの配置:波長を考慮したビア間隔 など

5. EMC測定

⇒IC周辺のノイズ低減設計により、不要輻射を根元から断つ

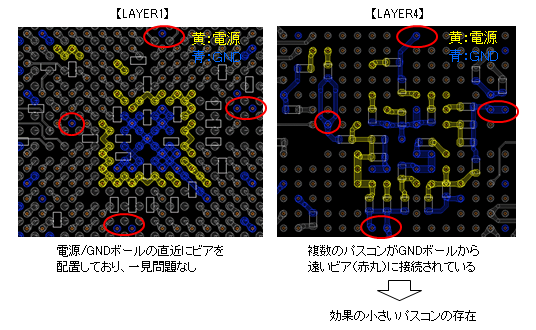

事例2 高速ICのパスコン数量半減を実現したコストダウン設計

お客様のご要望

- 高速ICに大量なコンデンサがあり削除したいが、どれを削除すべきか不明

- コンデンサ削除前後の電源特性を定量的に検証したい

- 難しいかもしれないが、何とかパスコン数量を半減したい

実施内容

1. 基板レイアウトの検証

- パスコン半減のポイント

- パスコン削減戦略

効果の小さいパスコンをピックアップし、削除する - ビア配置変更

GND、電源ボールからビアまで1mm以上離れないようにビア配置 - ビアとパスコンの接続

全てのパスコンをビアの直近に配置し、パスコンの効果を大きくする。

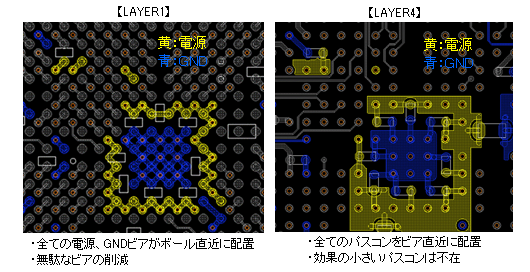

2. 基板レイアウトの修正

パスコン半減のポイントに留意して基板レイアウト設計

⇒パスコン半減のポイントを守り、0.1uFコンデンサを21個から9個に削減

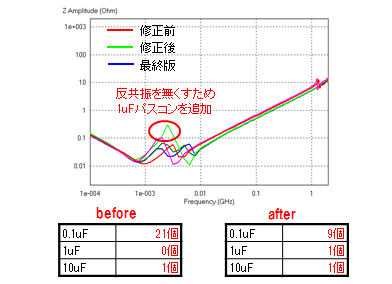

3. 電源インピーダンス解析

電源インピーダンス解析により、修正前後の電源特性を定量比較

- 修正後基板に反共振(赤丸)⇒リスク回避のため1uFコンデンサを1個追加

- 10MHz以上では、最終版の方がインピーダンスは低い

⇒解析結果を分析し、特性確保のために必要であればパスコンを追加

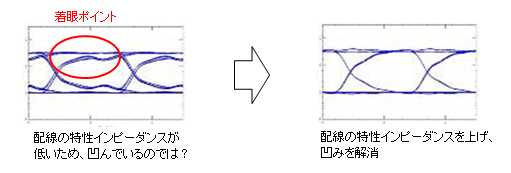

事例3 HDMIコンプライアンス試験合格に向けた配線特性、信号品質改善

お客様のご要望

- HDMIのコンプライアンス試験不合格となった原因の解明

- 課題解決策の提案、具現化によるコンプライアンス試験合格

実施内容

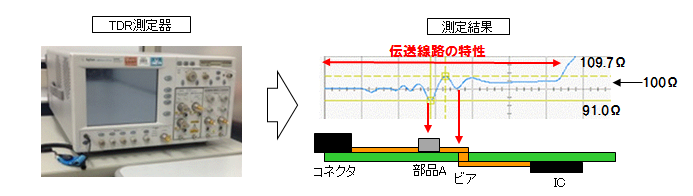

1. TDR(time domain reflectometry)測定器による配線特性評価

⇒特性インピーダンスの低下箇所を特定

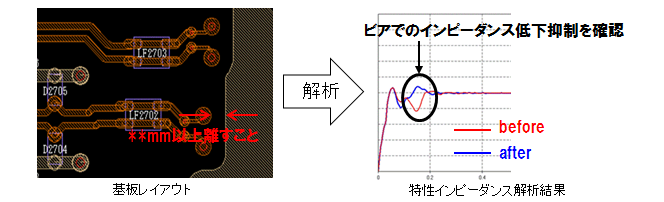

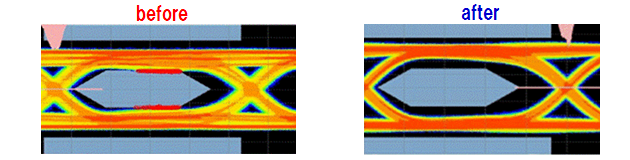

2. プリント基板のHDMI配線改善検証

改善案の一例:ビア周辺GNDプレーンの距離調整(GNDとの結合を抑えるため)

⇒特性インピーダンスの低下箇所の改善効果を解析で確認

3. コンプライアンス試験

⇒コンプライアンス試験合格を確認

事例4 多様な接続構成を具現化したDDR3-1866設計

お客様のご要望

- ひとつのLSIで、メモリ使用数を2個、4個、8個の3パターンで設計したい。

- コストを考慮し、4層貫通基板で設計したい。

- 開発期間が短いので、メモリ設計の失敗は許されない。確実に動作させたい。

- 回路、基板レイアウトの設計を任せたいので、色々提案して効果を検証してほしい。

実施内容

1. トポロジ検討

- 様々なパターンのトポロジを提案。解析により最適なトポロジを決定

- 解析結果を検証し、配線幅、配線間隔を決定

⇒解析結果から問題箇所の原因を推定。改善案を提案、検証して波形品質確保。

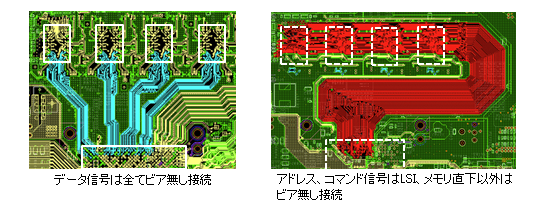

2. LSIとメモリの接続検証

- 波形品質を悪化させるビアの数を最小限にするにはどうすれば良い?

ポイント:LSIとメモリの信号引出し順番を考慮してボール配置を検討(下記例はメモリ4個使いのレイアウト)

⇒ビアの数を最小限にできるボール配置、基板レイアウトを提案、具現化

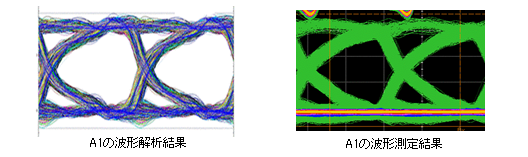

3. CADレイアウトを活用した信号波形解析

- トポロジ解析では検証できない、同時スイッチングを考慮した詳細解析により、CADレイアウトの信憑性を確認

⇒CADレイアウトに問題ないことを確認。実測波形との相関もあり

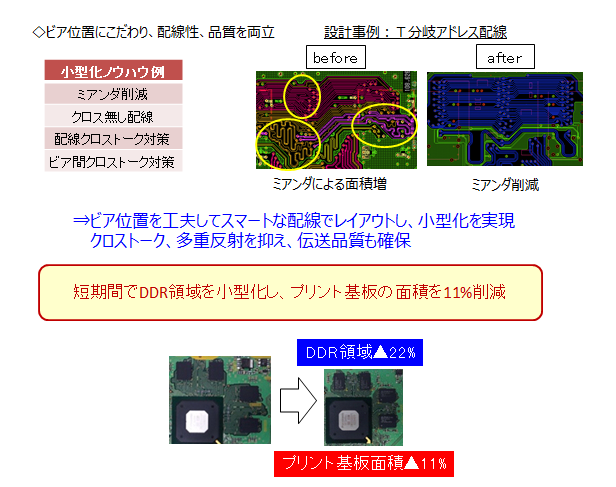

事例5 DIGAのDDR3領域小型化事例

お客様のご要望

- DDR3領域を小型化し、基板のコストダウンを実現したい

- 商品への適用のため、できるだけ早く設計を完了したい

実施内容

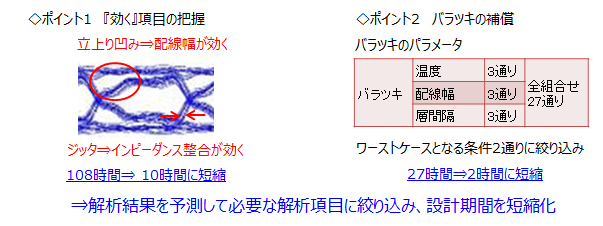

1. 解析項目の絞込みによる設計期間の短縮化動作原理に基づき解析結果を予測

2. プリント基板の小型化