低ノイズ設計

お客様の課題が、「EMC対策期間の短縮」である場合、後工程でのEMC対策支援では根本的な解決にはなりません。EMC性能の実現のためには、EMC特性に優れる半導体の選定と、電子回路設計からプリント基板設計の各工程での配慮が必要になります。さらに、その一連の取り組みをお客様の「商品設計のしくみ」として定着させることが望まれます。プロダクト解析センターではしくみ作りからのサポートも行っています。

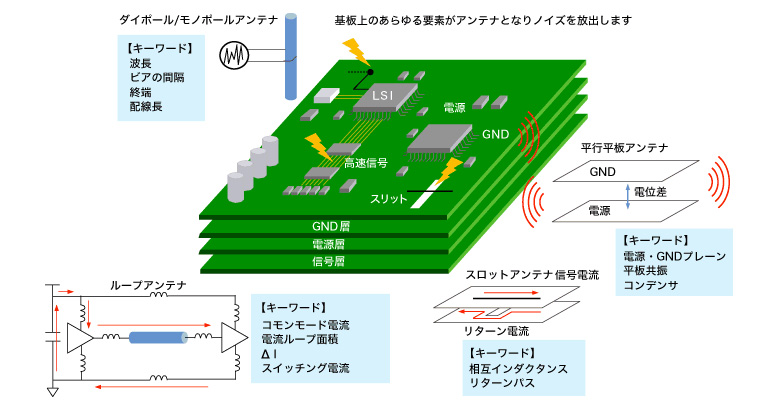

ノイズを抑えた基板に

基板スリットからのノイズ放射や意図しない電流ループによるコモンモードノイズなど、回路図には現れない様々なリスクを予測し、EMC品質の高いプリント基板を設計します。また、私たちの「構想設計」では、回路設計段階や基板仕様検討段階からのEMC設計も行っています。

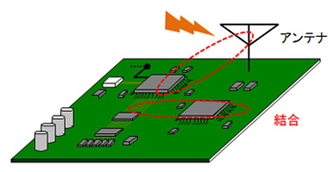

相互干渉の回避

基板スリットからのノイズ放射や意図しない電流ループによるコモンモードノイズなど、回路図には現れない様々なリスクを予測し、EMC品質の高いプリント基板を設計します。また、私たちの「構想設計」では、回路設計段階や基板仕様検討段階からのEMC設計も行っています。

機器内部の自家中毒イメージ

部品配置/配線戦略のポイント

プロダクト解析センターは、EMC試験(認証)や製品レベルでのEMC対策、サイト管理支援、教育訓練なども行っています。詳しくはEMCのページご覧ください。