リーン設計事例

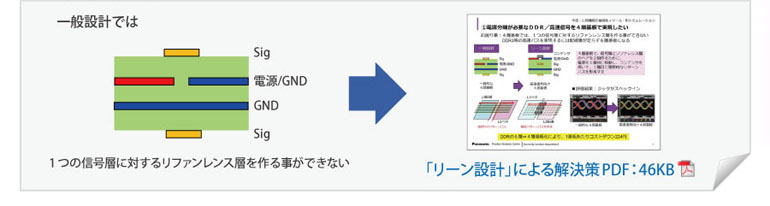

事例1 電源分離が必要なDDR/高速信号を4層基板で実現したい。

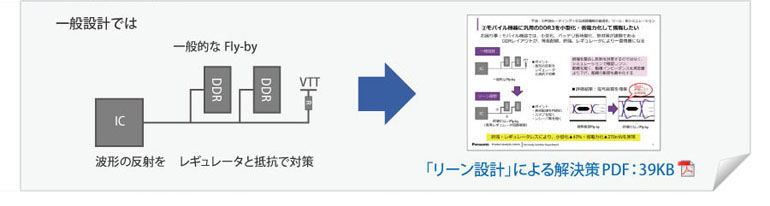

事例2 モバイル機器に汎用のDDR3を小型化・省電力化して搭載したい。

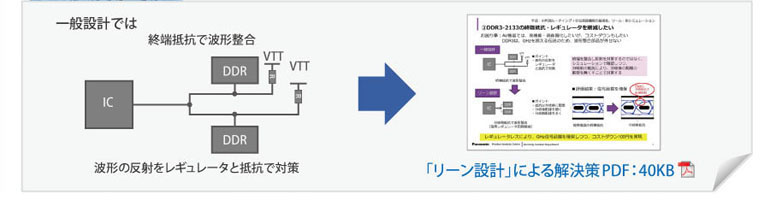

事例3 DDR3-2133の終端抵抗・レギュレータを削減したい。

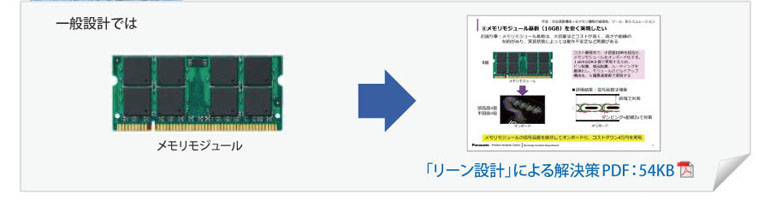

事例4 メモリモジュール基板(16GB)を安く実現したい。

事例5 8層基板やビルドアップ基板が推奨のDDR3を低層化したい。

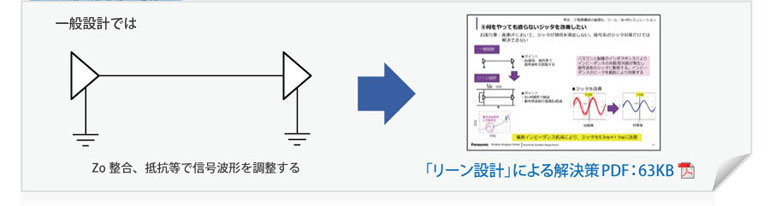

事例6 何をやっても直らないジッタを改善したい。

事例7 設計検証時は合格だったが、量産品でジッタがスペックアウトした。

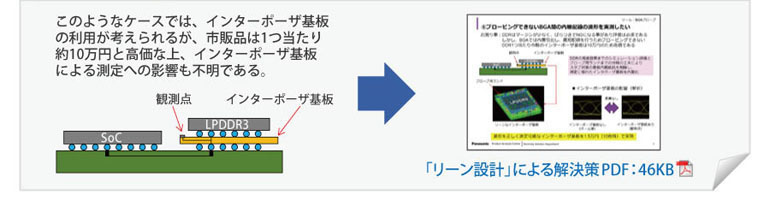

事例8 プロービングできないBGA間の内層配線の波形を実測したい。

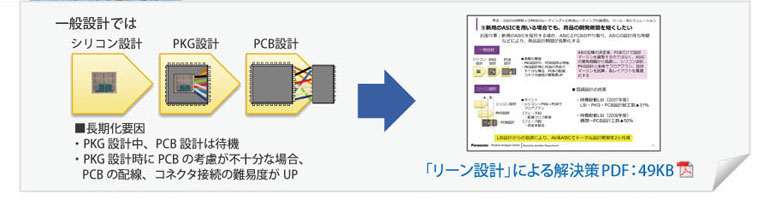

事例9 新規のASICを用いる場合でも、商品の開発期間を短くしたい。

事例10 3Gbps信号の基板間ケーブル伝送を安く実現したい。