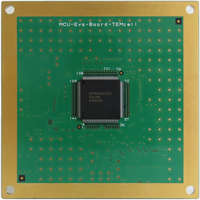

基板設計へのこだわり

半導体のEMC試験では、半導体を実装するプリント基板の影響を受けるため、適切なデカップリングや、パターンのインピーダンス・平衡度などを考慮したプリント基板設計が求められます。 プロダクト解析センターでは、プリント基板設計チームを有しており、IEC 61967-1などに準拠した標準試験プリント基板の設計・製作から、試験結果の報告まで、一連のプロセスをサポートいたします。

IEC 61967-1、およびIEC 62132-1では評価に使用するプリント基板の共通ルールを記述しています。 AEC-Q100やSAE J1752もこの規格に準拠して基板を作成します。 これにより、プリント基板の仕様(寸法、レイアウト、層構成など)による評価結果の影響を最小化(一定化)し、異なるIC間のEMC性能の比較が可能となります。

弊社では標準プリント基板の設計による影響を最小限に抑えるための検証を行っております。

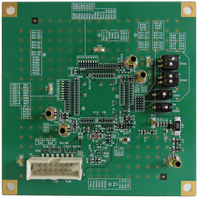

半導体(IC / LSI)単体のノイズを確実に評価するためには、プリント基板の作り込みが欠かせません。 基板の作り込みが悪いと、例えばDCDCコンバータのスイッチングノイズが見えてしまい、半導体単体でのノイズを定量化できなかったり、パターン間の結合により予期せぬ誤動作が発生してしまうことがあります。

弊社では、周辺回路の影響を考慮したプリント基板設計により、最適な標準プリント基板をご提供するのはもちろんのこと、お客様のアイディア、想いを実現すべく、LSI動作に必要な評価治具の設計や評価環境の構築も実施いたします。